The WARP v3 hardware platform has reached end of life and is no longer available. The original product page is archived below.

The Mango team continues to support the 802.11 Reference Design and WARPLab Reference Design for WARP v3 hardware. Technical support is provided via the WARP Forums.

Please contact us with any questions.

CM-PLL: WARP v3 Clock Module with on-board PLL and VCXO

The CM-PLL is a clock module for WARP v3 which provides a high-quality clock to the WARP v3 clock buffers whose frequency is locked to an local or external reference. The CM-PLL module integrates a PLL, low-jitter VCXO and reference clock multiplexer.

Key Features

- Analog Devices AD9511 PLL

- Texas Instruments LMK03004 clock mux

- 80MHz low-jitter voltage-controlled oscillator (VCXO)

- 6-position DIP switch for run-time configuration

- Reference clock input from:

- MMCX jack

- Board-to-board header

- WARP v3 TCXO

Clock and FPGA I/O

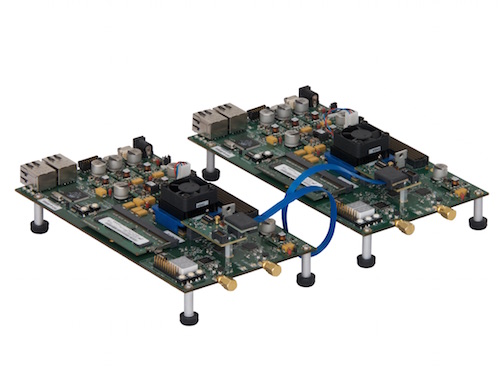

The CM-PLL module has two 10-pin connectors. Each connector allocates 4 pins to FPGA I/O and 1 pin for the PLL reference clock. One connector has a reference clock input, one has an output driven by a buffered copy of the reference clock. These connectors enable synchronizing multiple WARP v3 kits in a daisy-chain configuration. There are various options for the board-to-board cables. Refer to the CM-PLL User Guide for details.

The photo below illustrates two WARP v3 kits equipped with CM-PLL modules in a daisy-chain configuration. The single cable connection synchronizes the WARP v3 clocks and routes 4 FPGA signals for shared triggering of the FPGA designs.