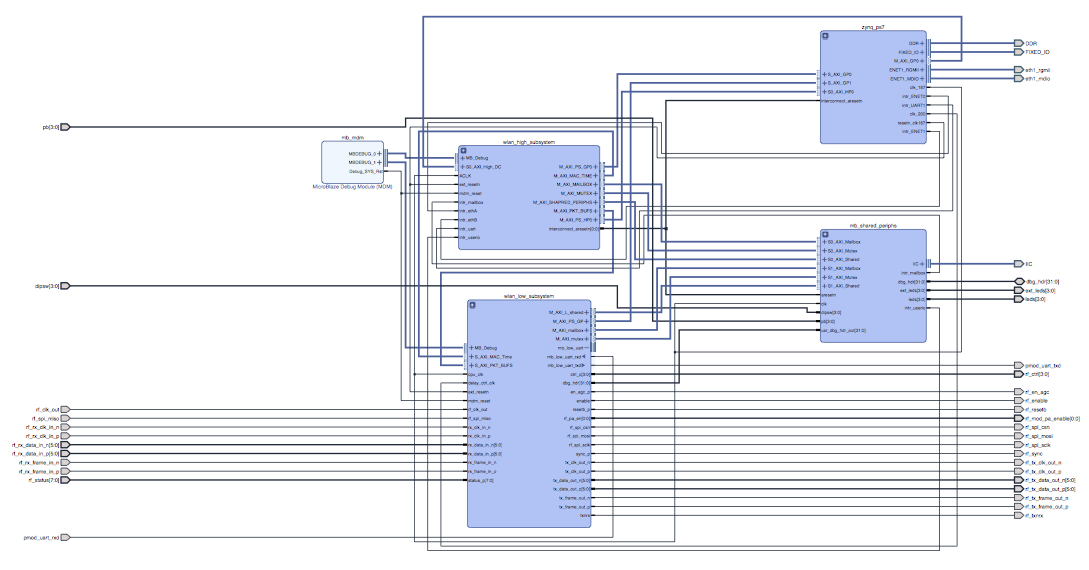

802.11 MAC/PHY - FPGA Design

Our reference FPGA Design integrates our 802.11 IP cores, MicroBlaze CPUs and peripheral interfaces. The FPGA Design is ready for immediate use on reference hardware platforms. The design can also be ported to custom hardware.

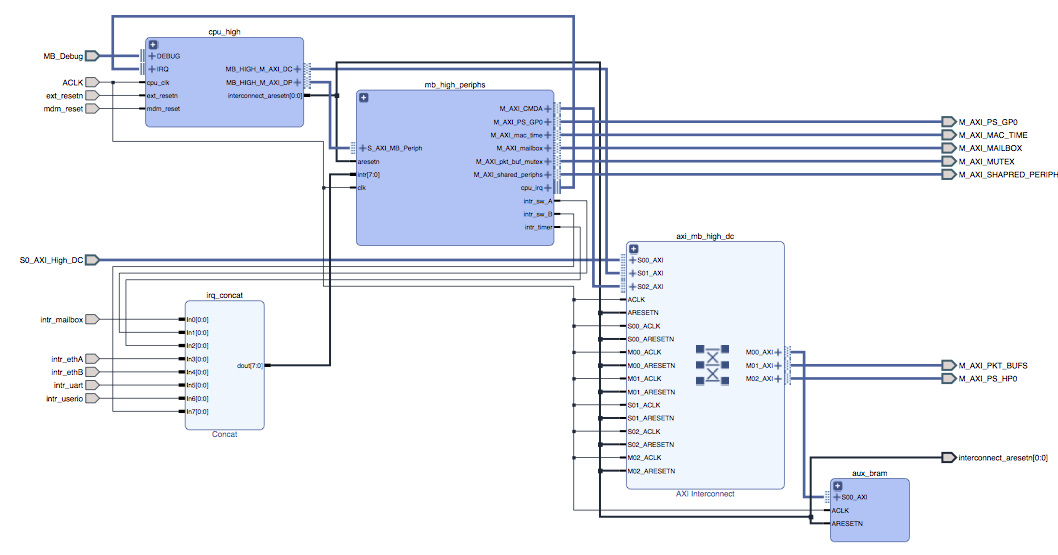

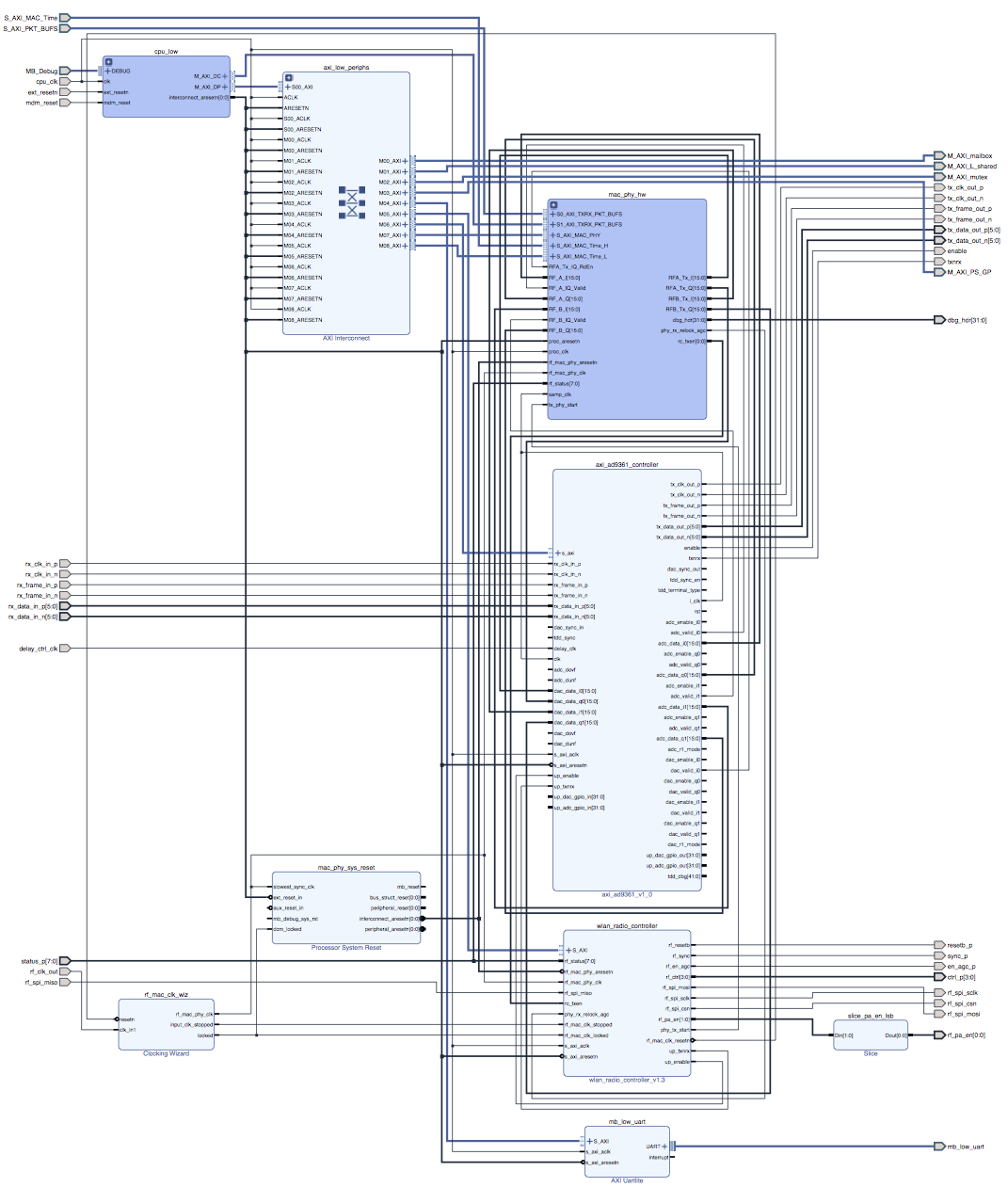

The FPGA Design is implemented as a Xilinx Vivado IP Integrator (IPI) block diagram. The IPI design integrates:

- Mango 802.11 PHY Tx, PHY Rx and MAC support cores

- Radio control/interface core

- Two Xilinx MicroBlaze 32-bit CPUs running MAC software

- Mailbox and mutex for inter-processor communication

- Ethernet MACs and DMAs for wired/wireless bridging and control plane interfaces

- Dev board peripheral controllers (UART, user I/O, etc.)

| IPI Block Diagram | ||

|---|---|---|

Reference Hardware Platforms

We provide reference FPGA designs for the hardware platforms listed below. Refer to the user guide for more details on hardware options.

Our 802.11 design can be ported to custom hardware. The required development effort depends on the new platform’s similarity to our reference platforms. The Mango team has experience working with customers to port our design to new hardware platforms.

Analog Devices ADRV9361

The ADI ADRV9361 platform integrates a Xilinx Zynq SoC and the AD9361 radio transceiver. This platform is best suited for benchtop development.

Our reference design supports the following RFSOM hardware:

- ADRV9361 SDR module - RF System-on-Module with AD9361 transceiver and Xilinx Zynq 7Z035 processor

- ADRV1CRR-FMC FMC carrier - dev board which powers the ADRV9361 module and provides provides peripherals and connectivity

- AD-PZSDR2400TDD-EB module - 2.4GHz PA/LNA module for FMC carrier (supported, not required)

Support for the ADRV1CRR-BOB breakout carrier is coming soon.

(The ADRV9361 hardware is also known as RFSOM and was previously known as Avnet PicoZed SDR).

National Instruments USRP E320

The NI USRP E320 integrates a Xilinx Zynq SoC, ADI AD9361 radio transceiver, and flexible RF front-end, all packaged in a rugged enclosure. This platform is suited for benchtop development or mobile experiments.